Vending Machine Code In Verilog

Simulation of VHDL code for a vending machine. Where the instantiation and wires / regs don't resemble the source code like in VHDL. Yeah, VHDL is better than Verilog any day of the week;) This goes doubly for a beginner, who may not know the basics required to start the testbench. Nov 07, 2013 Verilog Code for Vending Machine Using FSM. In this wending machine, it accepts only two coins, 5 point and 10 point. Whenever total of coins equal to 15 points, then nwpa signal will go high and user will get news paper. It will not return any coin, if.

Dnd 3.5 wealth by level. Module mooreverilogcode(out, in, rst, clk);output out;input in;input clk, rst;reg out;reg1:0 state;parameter s0=2'd0, s1=2'd1, s2=2'd2, s3=2'd3;always @(posedge clk or negedge rst)if(rst0) begin state=s0; out=0; endelse begincase (state)s0: begin out=0; if(in0) state=s1; else state=s0; ends1: begin out=0; if(in0) state=s1; else state=s2; ends2: begin out=0; if(in0) state=s3; else state=s0; ends3: begin out=1; if(in0) state=s1; else state=s2; enddefault: state=s0;endcaseendendmodule Verilog source codesRF and Wireless tutorials.

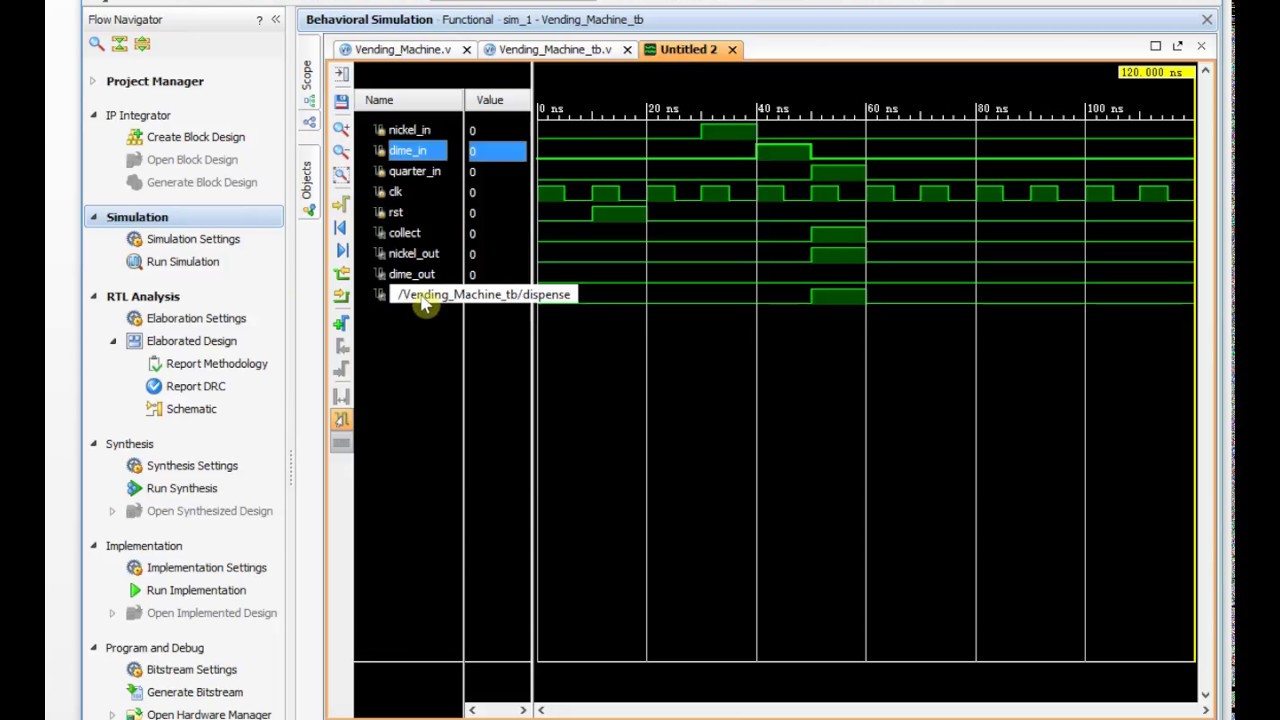

I am trying to build a finite state machine in verilog for a vending machine that accepts 5,10, 25 cents as inputs and then output a a soda or diet and also output the appropriate change(as the number of nickels). I am currently getting an error that says ERROR:HDLCompiler:806 - 'D:/Xilinx Stuff/FSM/FSM.v' Line 128: Syntax error near 'endmodule'.I am fairly new to verilog and whilst I get that this is probably a silly error like forgetting a semi-colon or something, I just cannot for the life of me find it. I'm not sure why you are using: always @(currentstate ((quarter ^ nickel) ^ dime))the standard coding style would be to use: always @(currentstate or quarter or nickel or dime)With Verilog 2001 or System Verilog you can use a comma separated sensitivity list as follows: always @(currentstate, quarter, nickel, dime)Finally in verilog 2001 and later, you can use a wildcard for combinatorial logic always blocks: always @(.)If you need to debounce your inputs or make sure no more than one of the coin signals is asserted at a time, that should probably be done outside of the state machine.